Obsah

AP2, IN2 Výpočetní systémy II

Zadání

(Procesory, jejich parametry a architektury. Architektura Intel. Vnitřní a vnější paměti a principy jejich funkce. Vstupní a výstupní zařízení počítače a jejich připojování)

Koncepce Johna von Neumanna

• RAM –- paměť pro čtení i zápis

• ROM –- paměť pouze pro čtení

• Paměť s přímým přístupem

• Paměť se sekvenčním přístupem

• Vnitřní (operační) paměť

• Vnější (periferní) paměť

• Registr

• V/V zařízení (I/O equipment)

• Řadič (Controller) – zařízení převádějící příkazy v symbolické formě (instrukce) na posloupnost

signálů ovládajících připojené zařízení

1945: Architektura „von Neumann“

IAS Computer: Priceton Institute for Advanced Studies

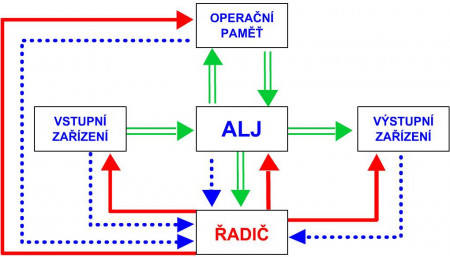

- Počítač obsahuje operační paměť, ALJ, řadič, V/V zařízení.

- Předpis pro řešení úlohy je převeden do posloupnosti instrukcí.

- Údaje a instrukce jsou vyjádřeny binárně.

- Údaje a instrukce se uchovávají v paměti na místech označených adresami.

- Ke změně pořadí prováděných instrukcí se používají instrukce podmíněného a nepodmíněného skoku.

- Programem řízení zpracování dat probíhá v počítači samočinně.

- Podstatným rysem této architektury je fakt, že instrukce a data jsou (oproti například Harvardské architektuře) uložena ve stejné paměti (viz Wikipedia).

- zelená (dvojitá) šipka - tok dat

- červená (klasická) šipka - povely

- modrá (prerušovaná) šipka - z V/V stavová hlášení, z paměti instrukce

Procesory, jejich parametry a architektury

Procesor je synchronní stroj řízený řadičem.

• Základní frekvence = takt procesoru

• Strojový cyklus = čas potřebný k zápisu (čtení) slova z paměti (např. 3 takty)

• Instrukční cyklus = čas potřebný pro výběr a provedení instrukce

Instrukce se skládá z operačního kódu a nepovinných adres operandů (1 nebo 2 adresy)

Součásti procesoru:

- řadič nebo řídicí jednotka, jejíž jádro zajišťuje řízení činnosti procesoru v návaznosti na povely programu, tj. načítání instrukcí, jejich dekódování (zjištění typu instrukce), načítání operandů instrukcí z operační paměti a ukládání výsledků zpracování instrukcí.

- sada registrů (v řadiči) k uchování operandů a mezivýsledků. Řadič obsahuje celou řadu rychlých pracovních pamětí malé kapacity, tzv. registrů, které slouží k jeho činnosti. Registry dělíme na obecné (pracovní, universální) a řídící (např. registr adres instrukcí, stavové registry, indexregistry). Velikost pracovních registrů je jednou ze základních charakteristik procesoru.

- jedna nebo více aritmeticko-logických jednotek (ALU – Arithmetic-Logic Unit), které provádí s daty příslušné aritmetické a logické operace.

- některé procesory obsahují jednu nebo několik jednotek plovoucí čárky (FPU), které provádí operace v plovoucí řádové čárce

Dělení procesorů:

- podle délky operandu v bitech tj. šířka operandu, který je procesor schopen zpracovat v jednom kroku. (16bitový, 32bitový, 64bitový…)

- podle struktury procesoru RISC, CISC, jednoduché procesory (ochrana paměti), jednočipový mikropočítač (samostatně činný procesor, v perifériích), DSP (digitální signálový procesor je procesor zaměřený na zpracování signálu)

RISC, CISC, Pipelining

CISC (Complex Instruction Set Computer)– plná sada instrukcí, větší instrukce vykonávány jako celek.

RISC a CISC procesory podle vnitřní architektury a počtu instrukcí, které procesor umí vykonávat. Současné procesory Intel a kompatibilní jsou vnitřně RISC, kde za pomoci mikroinstrukcí vykonávají složité CISC instrukce a umožňují aktualizaci řídícího mikrokódu. Původně lepší možnosti RISC procesorů byly překonány masivními investicemi firmy Intel získanými masivní výrobou procesorů do osobních počítačů, takže současné CISC procesory překonávají RISC.

Využívají řetězení instrukcí (pipelining).

Pipelining neboli zřetězené zpracování, či překrývání instrukcí. Základní myšlenkou je rozdělení zpracování jedné instrukce mezi různé části procesoru a tím i dosažení možnosti zpracovávat více instrukcí najednou. Fáze zpracování je rozdělena minimálně na 2 úseky.

- podle počtu jader

Zásadním parametrem, který je u procesoru důležitý, je frekvence práce jeho jádra.

Důležitým faktorem celkového výkonu procesoru je tedy nyní i velikost vyrovnávací paměti procesoru, která se označuje cache.

Cache – Je zařazena mezi dva subsystémy s různou rychlostí a vyrovnává tak rychlost přístupu k informacím. Cache může být hardwarová a softwarová.

Hardwarová cache

Cache paměť v procesoru ukládá kopie dat přečtených z adresy v operační paměti. Pokud při čtení obsahu slova z adresy v paměti je tato položka nalezena v cache paměti, je její obsah přečten z cache paměti a ne z operační paměti (angl. cache hit). Mezi procesorem a cache pamětí se přenášejí jednotlivá slova, mezi cache pamětí a operační pamětí se přenášejí rámce slov o velikosti několikanásobku velikosti slova procesoru. Protože asi 90 % operací procesoru je čtení paměti, většinou sekvenční, je tímto způsobem dosaženo větší propustnosti dat z operační paměti do procesoru, tím i vyššího výpočetního výkonu.

Vyrovnávací paměť procesoru bývá dvojstupňová. Část paměti o malé kapacitě je přímo součástí procesoru a je stejně rychlá, jako vlastní procesor (značí se L1). Další paměť, pomalejší, ale s větší kapacitou, je mezi procesorem a operační pamětí, dnes se již umisťuje do pouzdra s procesorem (značí se L2). Protože cena paměti stoupá s její rychlostí (a samozřejmě s kapacitou), je možné tímto uspořádáním najít kompromis mezi cenou a rychlostí.

Softwarová cache

Fáze procesoru:

výběr instrukce z paměti → provedení instrukce → přerušení, …

Výběr instrukcí je řízen registrem:

- čítač instrukcí

- PC (Program Counter)

- IP (Instruction Pointer, alternativní název k PC)

Počítač pracuje ve dvojkovém doplňkovém kódu.

registry:

A – střádač – 8bitový (Accumulator)

PC – čítač instrukcí – 16bitový

paměť:

adresovatelná jednotka = slabika

data – 8bitová

Instrukční soubory (pro programátora viditelné):

LDA adresa – Load A Direct

- naplní registr A obsahem slabiky z paměti

- uložení instrukce v paměti:

| operační znak | 16bitová adresa paměti |

| 3Ah | nižší slabika adresy / vyšší slabika adresy |

STA adresa – Store A Direct

- uložení registru A do paměti

- uložení instrukce v paměti:

| operační znak | 16bitová adresa paměti |

| 32h | nižší slabika adresy / vyšší slabika adresy |

JMP adresa – Jump Unconditional

- nepodmíněný skok na adresu

- uložení instrukce v paměti:

| operační znak | 16bitová adresa paměti |

| 0DAh | nižší slabika adresy / vyšší slabika adresy |

Instrukce a mikroinstrukce

Interní registry – pro programátora neviditelné

- IR: instrukční registr (8bit), je napojen na dekodér instrukcí

- DR: datový registr (8bit), určen pro čtení/zápis dat v paměti

- AR: adresový registr (16bit), adresa pro četní/zápis v paměti

- TA = (TAH, TAL) – Temporary Address Register (16bitový), skládá se z: TAH (TA High - 8 bitů),

TAL (TA Low - 8 bitů)

Fáze instrukce LDA adresa (mikroinstrukce)

PC → AR, 0→WR, DR→IR výběr operačního znaku

PC + 1 → AR, 0 → WR, DR → TAL výběr operandu

PC + 2 → AR, 0 → WR, DR → TAH výběr operandu

TA → AR, 0 → WR

DR → A provedení instrukce

PC + 3 → PC provedení aktualizace PC

Fáze aritmetické instrukce INR r (Increment Register)

r + 1 → r

PC + 1 → PC

Zásobník (Stack):

struktura LIFO (Last In, First Out)

registr SP (Stack pointer)

instrukce PUSH, POP

V/V operace:

OUT zapíše obsah A na V/V sběrnici

IN přečte obsah V/V sběrnice do A

START zahájí V/V operaci

FLAG adresa skok na adresu, není-li operace hotova

Přerušení

Architektura Intel

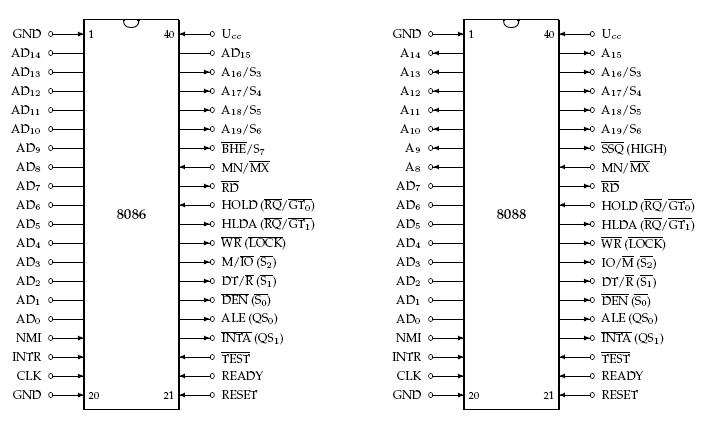

Architektura procesoru Intel 8086 a 8088

Procesor 8086

- 16bitový procesor

- 1978–1982

- základní procesor řady INTEL x86

- frekvence max. 10 MHz

Procesor 8088

- 16bitový procesor do 8bitového prostředí

- 1979–1982

Zapojení procesoru

INTR Signál žádosti o maskovatelné přerušení.

TEST Signál testovatelný instrukcí WAIT. Při TEST=L program pokračuje další instrukcí.

NMI Signál nemaskovatelného přerušení.

RESET Signál okamžitě ukončující aktivitu CPU a předávající řízení instrukci na adrese 0FFFF0h.

LOCK Uzamčení sběrnice pro procesor, který nastavil LOCK=L instrukčním prefixem LOCK.

M/IO Rozlišuje, zda adresa patří paměti nebo V/V v procesoru 8086.

Typ dat zpracovávané procesory Intel

Procesory 8086 a 8088 používají k ukládání dat metodu Little-Endian (V tomto případě se na paměťové místo s nejnižší adresou uloží nejméně významný bajt (LSB) a za něj se ukládají ostatní bajty až po nejvíce významný bajt (MSB)).

příklad uložení 32bitového čísla 4A3B2C1D na adresu 100:

| … | 100 | 101 | 102 | 103 | … |

| … | 1D | 2C | 3B | 4A | … |

Big-Endian, používající se u jiných procesorů – V tomto případě se na paměťové místo s nejnižší adresou uloží nejvíce významný bajt (MSB) a za něj se ukládají ostatní bajty až po nejméně významný bajt (LSB) na konci.

příklad uložení 32bitového čísla 4A3B2C1D na adresu 100:

| … | 100 | 101 | 102 | 103 | … |

| … | 4A | 3B | 2C | 1D | … |

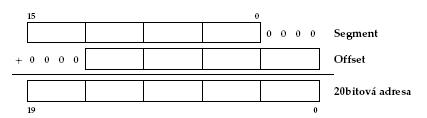

Adresace paměti v procesorech 8086 a 8088

Adresu zapisujeme ve tvaru segment:offset

takže v podstatě sečteme segment a vpravo posunutý (o jeden řád) offset a dostaneme rozsah adresy.

příklad: Zápis 01A5:001216 představuje tedy dvacetibitovou adresu 01A6216

Zásobník pak funguje jako segment a jeho položky jsou offset. V jednom segmentu tedy nevytečeme dál jak 64 kB.

Příznakový registr procesoru 8086

V tomto 16bitovém registru se nastavuje chování procesoru a různé stavy při výpočtech. Např. (sedmý bit – ZF (Zero Flag) je nastaven při nulovém výsledku právě dokončené operace. Osmý bit – SF (Sign Flag) je kopií znaménkového bitu výsledku operace.)

Zásobník

SS – stack segment

SP – stack pointer

SS:SP – přesné misto v SS zásobníku

Přerušení v 8086

Vnější (gen. technickými prostředky)

- nemaskovatelná (signál NMI)

- maskovatelná (signál INTR)

Vnitřní (gen. programově)

- instrukcí INT n

- chybou při běhu programu

Každé přerušení je identifikováno svou hodnotou.

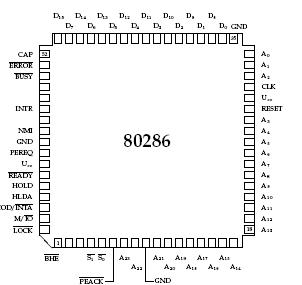

Architektura procesoru Intel 80286

- 16bitový procesor,

- od 1982, cca do 1990,

- frekvence 6–16 MHz,

- nové počítače PC AT,

- 24bitová adresová sběrnice, tj. 16 MB RAM.

zapojení

CAP Mezi tento vývod a vývod GND musí být zapojen kondenzátor kapacity 0,047 μF ±20% 12V

vyhlazující nežádoucí napěťové zákmity.

PEREQ Signálem koprocesor žádá procesor o vyslání operandu.

PEACK Signálem procesor oznamuje koprocesoru, že vysílá operand.

BUSY Aktivní úroveň signálu oznamuje, že koprocesor provádí výpočet. Signál je testován instrukcí WAIT.

ERROR Signálem koprocesor oznamuje chybový stav.

Režimy procesoru 80286

Reálný režim

- Je nastaven po inicializaci procesoru.

- Je slučitelný s procesorem 8086.

Chráněný režim

- Zapíná se programově z reálného režimu.

- Adresuje 16MB reálné paměti a 1GB virtuální paměti.

- Poskytuje prostředky 4 úrovňové ochrany.

- Nelze se vrátit z chráněného režimu zpět do reálného.

Rozdíl reálného režimu oproti 8086

8086:

F F F F

+ F F F F

0 F F E F (tj. 65 51910, 64 K je 65 536)

80286:

F F F F + F F F F

1 0 F F E F (tj. 1 MB + 65 51910)

- příznakový registr se od 8086 mírně liší, především se objevily nové položky v registru (např. IOPL (I/O Privilege Level) určuje úroveň oprávnění, při které může proces ještě provádět V/V instrukce.

- nový příznakový registr MSW (Machine Status Word)

především pro informace o režimu. Využito pouze 4 bity z 16

Úrovně oprávnění

úrovně oprávnění (privilege levels) – v příznakovém registru na 2 bitech

nejvyšší po nejnižší

0 1 2 3

úroveň 0 . . . jádro operačního systému (řízení procesoru, V/V operací),

úroveň 1 . . . služby poskytované operačním systémem (plánování procesů, organizace V/V, přidělování prostředků),

úroveň 2 . . . systémové programy a podprogramy z knihoven (systém obsluhy souborů, správa knihoven),

úroveň 3 . . . uživatelské aplikace.

Adresace paměti v chráněném režimu

Virtuální adresa až 1 GB

Ta se skládá z 16bitového Selektoru a 16bitového offsetu.

Selektor obsahuje obsahuje ale adresu na 13 bitech (další 3 nesou info o úrovni oprávnění atd.).

Adresa ze selektoru ukazuje do tabulky (GDT/LDT - obsahuje 2^13 položek).

V této tabulce, která popisuje segmenty v reálné paměti, je na jednom řádku (64 bitů) info o segmentu – 1 B, kde segment začíná tzv. báze segmentu – 3 B , limit segmentu – 2 B a 2 B jsou prázdné.

Z báze segmentu a offsetu se složi 24 bitová reálná adresa. → 16 MB

Registry GDTR a LDTR – kde jsou umístěny tabulky GDT a LDT.

Architektura procesoru Intel 80386

Procesor Intel 80386

- 32bitový procesor,

- od 1986 do cca 1994,

- 16 MHz až 40 MHz,

- „zakladatel“ architektury IA-32,

- 32bitová adresová sběrnice, tj. max. 4 GB RAM,

- 32bitová datová sběrnice,

- alternativní název i386DX,

- varianta 386SX s 16bitovou datovou a 24bitovou adresovou sběrnici,

- matematický koprocesor zvlášť i387,

- i386SL pro laptop počítače, nižší spotřeba.

Architektura procesoru Intel 80386

- Selektor je stejný jako v 80286.

- Offset je 32bitový.

- Limit segmentu můžeme mít velikost až 4 GB – 1.

- Báze segmentu je 32bitová (tj. 0 až 4 GB – 1).

- Logická adresa (v terminologii 80286 se nazývá virtuální adresa) je složena z 16bitového selektoru

a 32bitového offsetu (tj. adresuje 64 TB virtuální paměti). Tato adresa je algoritmem segmentační

jednotky převedena na lineární adresu.

- Lineární adresa je 32bitová (tj. adresuje 4 GB). Není-li v činnosti stránkovací jednotka, potom

lineární adresa ukazuje už přímo do fyzické paměti.

- Fyzická adresa je transformována činností stránkovací jednotky z lineární adresy. Je rovněž 32bitová

(tj. adresuje 4 GB fyzické paměti). Není-li stránkovací jednotka zapnuta, je fyzická adresa totožná

s lineární adresou.

Stránkování

logická adresa → lineární adresa → fyzická adresa

Rámec a stránka o velikosti 4 kB.

Pro využití se musí zapnout stránkování v procesoru.

Architektura procesoru Intel 80486 (i486)

Oproti 386 je rozšířen o:

- jednotku operací v pohyblivé čárce (Floating point registr)

- interní vyrovnávací paměť (Internal Cache - pro data i instrukce 8KB)

- novou technologií blízkou RISC

opět doplněno o nové informace-položky v registrech (řídící, příznakový specifikátor stránkového adresáře…)

Architektura procesoru Intel Pentium

- Pentium z řecky penta, tj. 5,

- 32bitový procesor,

- od 1993 do 1999,

- 60 MHz až 300 MHz,

- od 1995: Pentium MMX, Pro, II, III, 4, D, Xeon,

- postupně se liší parametry: technologie např. 0,25 μm, velikostí cache, počtem jader…

V procesoru Pentium jsou integrovány všechny vlastnosti procesoru Intel486. Navíc poskytuje tato

významná rozšíření:

- superskalární architekturu,

- dynamické předvídání skoků,

- zřetězenou FPU,

- zkrácení doby provádění instrukcí,

- oddělené 8KB datové a instrukční vnitřní vyrovnávací paměti,

- protokol MESI pro řízení datové vyrovnávací paměti,

- 64bitovou datovou sběrnici,

- zřetězování cyklů sběrnice,

Předvídáni podmíněných skoků – (Branch Target Buffer)

Párování instrukcí

Režim správy systému (SMM) – podobný reálnému režimu. Nejsou v něm úrovně oprávnění. Lze zde provádět V/V operace a adresovat celou 4GB kapacitu fyzické paměti.

Architektura x86-64

x86-64 architektura

- 64bitový režim (long mode) – plně 64bitový režim

- kompatibilní režim – 32/16bitový režim, omezená kompatibilita s x86 (pouze chráněný

režim, žádný reálný, žádný V86 režim)

- x86 mode plná kompatibilita s x86 32/16bitovým režimem (vč. reálného režimu…)

Vnitřní a vnější paměti a principy jejich funkce

Vnější paměť představuje v architektuře počítače paměť určenou k trvalému ukládání informací (programů a dat), její obsah se vypnutím počítače neztrácí. K vnější paměti nemá procesor počítače zpravidla přímý přístup. Srovnej s vnitřní pamětí. Vnější paměť můžeme rozdělit na stálou a výměnou paměť. Operační systém k přístupu do vnější paměti používá ovladače zařízení a data jsou organizována do souborů podle pravidel použitého souborového systému. Výměnná paměť obvykle používá pro uložení dat výměnná datová média.

Mezi stálou vnější paměť počítače patří:

Pevný disk

Data jsou na povrchu pevného disku organizována do soustředných kružnic zvaných stopy, každá stopa obsahuje pevný anebo proměnný počet sektorů. Z důvodu efektivnějšího využití plochy disku je povrch většinou rozdělen do několika zón, každá zóna má různý počet sektorů na stopu. Sektor je nejmenší adresovatelnou jednotkou disku, má pevnou délku (donedávna 512 byte na sektor, nyní by se již po domluvě výrobců měly vyrábět disky s 4 KB na sektor). Pokud disk obsahuje více povrchů, všechny stopy, které jsou přístupné bez pohybu čtecí hlavičky, se nazývají cylinder (válec). Uspořádání stop, povrchů a sektorů se nazývá geometrie disku.

Adresa fyzického sektoru na disku se skládá z čísla stopy (cylindru), čísla povrchu a čísla sektoru.

Pro přístup k datům disku se používá starší metoda adresace disku CHS, která disk adresuje podle jeho geometrie (odtud název CHS - cylinder, head, sector). Hlavní nevýhodou je u osobních počítačů IBM PC omezená kapacita takto adresovaného disku (8 GB) a nutnost znát geometrii disku. U disků vyšších kapacit na rozhraní ATA, již neodpovídá zdánlivá geometrie disku skutečné fyzické implementaci (viz CHS).

Novější metoda pro adresaci disku je (u rozhraní ATA) LBA, sektory se číslují lineárně. Není třeba znát geometrii disku, max. kapacita disku je až 144 PB (144 miliónů GB). Rozhraní SCSI používá lineární číslování sektorů disku již od své první verze. Ostatní novější rozhraní již převážně metodu jako je LBA používají.

ATA ADM flash disk

Výměnná vnější paměť počítače patří:

- disketová jednotka

- CD jednotka

- DVD jednotka

- USB flash paměť

- Zip disk

Jako vnitřní paměť se u počítače označuje paměť, ke které má zpravidla procesor přímý přístup. Vnitřní paměť je zpravidla volatilní (nestálá) a po vypnutí počítače se její obsah ztrácí. Vnitřní pamětí se v architektuře počítače označuje paměť určená pro uložení strojového kódu běžících procesů a pro data těmito procesy právě zpracovávaná. Srovnej s vnější pamětí.

O správu obsahu vnitřní paměti, alokace paměti pro jednotlivé procesy se zpravidla stará operační systém, pro přístup do ostatních pamětí (video paměť, konfigurační registry apod.) jsou zpravidla použity ovladače zařízení.

Jako vnitřní paměť se zpravidla označuje:

- operační paměť

- cache paměť procesoru

- registry procesoru

- různé registry chipsetu (konfigurace počítače, řízení hardware, apod.)

- video paměť

Ukládání(rep. přístup) dat do vnitřní a vnější paměti se liší.

Do vnitřní paměti se přistupuje, jak již je zmíněno výše, buť přímo (registry, cache) anebo pomocí segmentace resp. stránkování (RAM).

Práce s vnější pamětí je ale jiná (musíme řešit implementační problém přístupu na disk – co nejrychleji číst data popřeházená na disku).

Existuje několik přístupů

- souvislá alokace datových bloků

soubor je na disku uložen v souvislé posloupnosti datových bloků

- alokace datových bloků pomocí zřetězeného seznamu

každý datový blok obsahuje data a ukazatel na následující datový blok

- alokace datových bloků pomocí tabulky

alokace datových bloků je založená na zřetězeném seznamu, ale ukazatele na následující datový blok jsou uloženy v tabulce FAT

- i-nodes

i-node je struktura, která obsahuje jak atributy souboru, tak adresy datových bloků, ve kterých je uložen obsah souboru

Více o přístupu k vnějšímu disku je v otázce Organizace souborů

Vstupní a výstupní zařízení počítače a jejich připojování

Rozhraní:

Centronics

Rozhraní Centronics (EPSON)

Paralelní rozhraní určené pro výstup informace

- Mechanická úroveň: Konektor Cannon 25kolíkový, na počítači je zásuvka.

- Elektronická úroveň:

- „0“ … 0V až 0.4 V – úroveň TTL

- „1“ … 2.4V až 5V – úroveň TTL

- Logická úroveň

RS-232-C (V.24), zapojení, signály

V.24 je rozhraní přizpůsobené pro telefonní linky:

- Mechanická úroveň: Konektor Cannon 25 nebo 9kolíkový, na počítači je zástrčka.

- Elektronická úroveň:

- „1“ … -15 V ÷ -3 V

- „0“ … 3 V ÷ 15 V

- Logická úroveň

Rozhraní IRPS (proudová smyčka)

- název převzatý z dálnopisné sítě

- až do 2 km

- proud 20, 40 mA

- chybí přesná definice

Nulmodem

Nulmodem je metoda propojení dvou počítačů pomocí RS-232 tak, že vodiče pro přenos a pro příjem jsou v obou směrech prohozené. Jedná se o klasické propojení počítačů pomocí „seriového kabelu“.

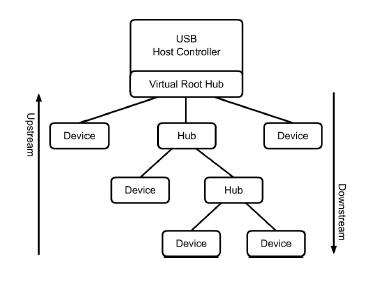

USB Universal Serial Bus

Idea:

- Všechna typická zařízení se stejně připojují na společnou sběrnici

- Náhrada připojení klávesnice, myši, RS232 zařízení, Centronics

- Snadnost použití

- Možnost připojování/odpojování bez vypnutí

USB 1.x (1996) v.1.0 1994-1996: Compaq, Intel, Microsoft a NEC, v.1.1 1998

Rychlost 1,5 Mb/s nebo 12 Mb/s

USB 2.0 (1999) Rychlost 480 Mb/s (teoretická rychlost)

USB 3.0 (2008) Přenosová rychlost je 5 Gbit/s. Nová technologie má 8 vodičů namísto původních 4, přesto zpětně podporuje USB 2.0.

Master/Slave protokol Komunikace je řízena/vyvolávaná počítačem (host), max. 127 zařízení.

Ochrana proti zkratu a přepětí Dovoluje se připojení/odpojení zařízení bez vypnutí počítače. Nutnost

ochrany proti elstat. výboji - člověk až 15 kV na koberci.

Zapojení

Čtyřdrátová sběrnice:

+5V

data -

data +

zem

Příklady V/V zařízení: myš, klávesnice,tablet, tiskárna, monitor, touchpad… prostě vše okolo samotného PC.

Co byste ještě měli znát?

- Měli byste znát rozdíl mezi Harvardskou architekturou a RISC architekturou.

- Měli byste umět vysvělit descriptory a úrovně v procesoru.

- Měli byste být schopni uvést nějaké instrukce v architektuře Intel.

Předměty

- FI:PB151 Výpočetní systémy, doc. Ing. Michal Brandejs, CSc.

Literatura:

Přednášky pro Výpočetní systémy - verze pro tisk, autorem je doc. Ing. Michal Brandejs, CSc.

Vypracoval

Petr Kott

petr.kott@post.cz

Otázku si přečetl pan RNDr. Vlastislav Dohnal a rámcově prošel. Jeho podněty pro doplnění textu, opravy nesrovnalostí a odstranění matoucích či k otázce se nevztahujících textů byly do otázky zaneseny. Tato kontrola je jen rámcová, stále se může stát, že v otázce zůstala zapomenutá chybka či nesrovnalost, vyučující za toto nenese odpovědnost, berte tuto rámcovou kontrolu jako formu pomoci od vyučujících pro studenty.

Diskuze

Myslim si, ze to je moc rozsahle, napr. vetu „CAP Mezi tento vývod a vývod GND musí být zapojen kondenzátor kapacity 0,047 μF ±20% 12V vyhlazující nežádoucí napěťové zákmity.“ si asi tezko nekdo vybavi u statnic Ale zase v tom autorovi nechcu nic mazat.

Ale zase v tom autorovi nechcu nic mazat.

:D jo, jasné je to copy ze script a proc to tam nechat/nenechat? Kdyz to smazu, usetrim cloveku asi 5s prace se ctenim. Kdyz ne, treba si to clovek zapamatuje a muze hodit velkou frajerinu pred komisi. Tak jako ja uz to ted nezapomenu… :D Ale davam samozrejme prostor pro edit. Budu rad, kdyz to nekdo nejak poopravi.. :) Jinak si nemyslim, ze by tam bylo moc nejakych „zbytecne extra“ informaci.

Spis mam takovy pocit, ze neco chybi… Jestli nekoho napada co, napiste a ja to opravim.

»Spis mam takovy pocit, ze neco chybi…

ja mam zase opacny pocit :)hlavne u toho Intelu mi to prijde zbytecne detailni, jen nejaky takovy prehled by byl podle me lepsi :)

Podle mě ještě určitě chybí von Neumannova architektura, co myslíte?

OKi, doplním, i když v zadání to není..

Zdar, len mensia poznamka, nepouziva nahodou Indel C2D, ci nove AMD uz RISC? Aspon tak sa mi zda / Google, Intel… A pan Brandejs ma tiez CISC pisany po Intal u486, tak neviem, chcelo by sa na to este pozriet.

Novější procesory Intel a AMD navazují na architekturu i386, takže je to pořád CISC.

Zdravím, nebylo by dobré doplnit ještě 486? zvláště když se u Pentia autor odkazuje na to, že Pentium má všechny vlastnosti 486.

Ahoj, co jeste chybi, aby byla otazka prohlasena za hotovou a mohla bych ji odeslat na kontrolu?

Podla mna tu chyba este podrobnejsi popis CISC a RISC architektur, nechapem preco sem autor daval take podrobnosti ako zapojenie Intel procesorov a toto vynechal…

Ja jsem osobne autorovi vdecna, ze se do te otazky vubec pustil a zpracoval ji, i kdyz je tam dle me hodne „zbytecneho“ textu a neni vyzdvihnuto to podstatne. Kazdopadne otazku odesilam na kontrolu, tak snad se dozvime, co v ni chybi a co je naopak nadbytecne

Tak jsem ještě doplnil nějaké maličkosti. Hlavně správu pamětí u každého procesoru. Snad už je to vše. No tota otázka dala zabrat..

Jinak ty Intely jsou docela pekne zpracovane na wikipedii http://cs.wikipedia.org/wiki/Intel . Myslim, ze tady je to zbytecne podrobne.

Mám návrh na (drobné) doplnění části „Fáze procesoru“

…

Základní principy činnosti procesoru jsou pro všechny řady procesorů Intel stejné. Pro jednoduchost bude princip demonstrovány na procesoru typu Intel 8086. .. nebo tak něco :)

Model našeho ukázkového počítače s 8086:

procesor je 8bitový = velikost zpracovávaných dat je 8bitů (slabika)

adresace paměti je 16bitová = max 64kB adresovatelné paměti

obsahuje registry: střádač A (8bit), čítač instrukcí PC/IP

počítač pracuje ve dvojkovém doplňkovém kódu

čítač instrukcí

- označován jako PC nebo IP.

- je podle něho řízen výběr instrukcí (obsahuje právě zpracovávanou adresu)

komentář k instrukční soubory:LDA

protože velikost dat může být maximálně 8bitů a my potřebujeme uložit 16bitovou adresu, ukládá se do dvou paměťových buněk. Takže třeba adresa 2104h se uloží jako 04 21.

komentář k fáze LDA

0→WR … načti obsah adresy uložené v AR do DR.

1→WR … zapiš na adresu uloženou v AR hodnotu uloženou v DR

DR→IR … dekódování instrukce jejíž operační znak je v DR

DR→A provedení instrukce …. //to je to, co jsme chtěli vlastně provést

*Chtěl jsem napsat 8080 (místo 8086) :)

Jinak v textu je u 286 .. a 1GB virtuální paměti. A u 386 pak 64TB virtuální paměti. Ale ty adresy se pak prolínají ne? jakože více virtuálních ukazuje na jedno místo ve fyzické paměti. Takže pořád adresujeme jen 16MB a 4GB. Přijde mi to tam pak matoucí, pokud se nepletu.

Ako nic v zlom, ale uz sem preboha nic nedoplnajte…tato otazka je uz aj taky taky moloch ze az :)

Skor mi pride, ze v casti „Vstupní a výstupní zařízení počítače a jejich připojování“ nieco chyba..kde su tam zmienene mysi, klavesnice, monitory, tiskarny a pod (pripojovanie PS/2 napr.), aspon to si ja pod tym predstavujem…nie rozsah napatia pri RS232…

To chce klid, uvarit si caj, otevrit si slajdy do Technickeho vybaveni (PV094) a precist si to tam. ;) (http://www.fi.muni.cz/usr/pelikan/Vyuka/Vyuka.html). Doporucuju, je to vynikajici alternativa k slajdum vypocetnich systemu, kde se tolik neresi jaky ma ktery pin napeti… :) Akorat si musi clovek najit ty spravne casti… (2, 3, 9, 12)

Jo, a jedna drobnost. MIPS a MFLOPS je rozdil. MIPS je u celociselnych a MFLOPS je u vypoctu v plovouci carce, takze ta poznamka (aspon mi to tak pripada) micha hrusky se svestkama, kdyz zminuje jeste operace v plovouci radove carce.

Súhlasím s Dušanom, otázka ide príliš do detailov, treba to trošku okresať.

Moje navrhované úpravy:

Tak čo si myslíte? Ak nebudú týmto návrhom negatívne ohlasy, tak sa pustím do editácie, nakoniec, vždy sa to bude dať vrátiť o pôvodného stavu…

ten text „Příklady V/V zařízení: Myš, klávesnice,tablet, tiskárna, monitor, touchPad,“ tam byl doplnen prave na podnet pana Dohnala, protoze je sice dobre popsat ta rozhrani a tak, ale clovek by opravdu mel zminit i co to vlastne to vstupni a vystupni zarizeni je.

Taky jsem pro ty upravy, uz jsem se snazila to aspon trochu strukturovat (nadpisy, boxiky, poznamky) a vyzdvihnout, co je podstatne. Je tam toho opravdu hodne a neda se to vse zapamatovat, kazdopadne, pokud to nekdo budete upravovat a nejak vyznamne do toho zasahovat (uplne mazat a predelavat casti), tak prosim oddelejte ten odstavecek o kontrole i celkovou informaci, ze je otazka zkontrolovana.

dalsi podnet pana Dohnala se jeste tykal vnejsi a vnitrni pameti:

„pridal bych, ze je rozdilne adresovani (u vnitrnich je typicky prime, u vnejsich - napr. disk - musite pouzit vice informaci).“ (zkraceno)

to jen, az to budes upravovat :)

a taky by mel byt kladen spis duraz na hlavni principy, viz dalsi pripominka, ktera byla do otazky uz dana:

„Ad cache procesoru - je hezke rici, ze je to dulezity vykonnostni prvek. Ale proc? Co to zrychluje?“

Ak to tu este niekto cita :), tak mi poradte, ako velmi sa to mam ucit, ked mam v komisii doktora Pelikana, ale na druhu stranu som na teoretickej?

Rozdíl mezi „Harvardskou architekturou a RISC architekturou“ – to by mě tedy zajímalo. Podle toho, jak to chápu, tak by bylo logičtější se ptát Harvard vs. Von Neumann a RISC vs. CISC. Podle mě může běžet RISC i CISC na architektuře, která je Harvardská i Von Neumamnnova.

S tím souhlasím, taky mi to nedávalo smysl.

Ty cache tu jsou poněkud nepřesné:

Tohle není pravda: „Původně lepší možnosti RISC procesorů byly překonány masivními investicemi firmy Intel získanými masivní výrobou procesorů do osobních počítačů, takže současné CISC procesory překonávají RISC.

Využívají řetězení instrukcí (pipelining).“

RISC je následníkem CISCu a překonává ho hlavně z důvodu snadnější paralelizace provádění instrukcí, které mají přibližně stejnou délku. Může se tak lépe plánovat a rozkládat instrukce do piplines.

Podotázka „Architektura Intel“ podle mne odkazuje spíše na x86 a x86-64, což jsou architektury v pravém slova smyslu. Jednotlivé architektury procesorů snad chtít nebudou, to by rovnou mohli chtít i vývoj procesorů AMD. Jde o to, že všechny PC používají architekturu x86 nebo x64 od Intelu nezávisle na tom, jestli je to procesor Intel nebo AMD. Snad pochopíte, co jsem tím myslel:)

Do I/O interfaces by se mohlo pridat Firewire, HDMI, eSATA, Ethernet. S tim se dnes asi potka clovek vic, nez s nejakym LPT portem, co si o tom myslite?

pri obrazku von Neumannovej architektury odporucam v legende zmenit nazvy sipok: zelena → dvojita, cervena → obycajna, modra → prerusovana

pri ciernobielom tisku (iny asi ani nie je mozny) je obrazok necitatelny

Edit: upravil som to v otazke